# A4032 Datasheet

Specifications are subject to change without notice.

©2020 YTL Technologies, Inc.

This document contains information that is proprietary to YTL Technologies, Inc.

Unauthorized reproduction of this information in whole or in part is strictly prohibited.

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2017.07.06 | 0.1     | Initial release                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 2017.10.18 | 0.2     | Delete raw data related descriptions and other unused descriptions. User cannot read raw data registers. Change register address of T8BAUD from $0x0186$ to $0x00E0$ .                                                                                                                                                      |  |  |  |  |  |

| 2018.03.12 | 3.0     | Modify reference voltage to 1.210V.  In order to obtain the best metering performance and temperature performance during normal metering, Bandgap Circuit must be configured according to the calculated result. The calculation method, please refer to Bandgap Circuit chapter.  Modify figure of Power, Clock and so on. |  |  |  |  |  |

| 2018.03.27 | 3.1     | Modify formula of offset Calibration of RMS.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 2018.05.31 | 3.2     | Modifying the formula of Phase Compensation.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 2018.09.01 | 3.3     | Add the power consumption range: +-10%.  Modify 3.3V power supply to 2.9~3.6V  Modify the typical value of the power down threshold to 2.7V, range 2.5V~2.9V  Modify the storage temperature to -55~150°C  Add register AnaCtrl0 (0x182) and AnaCtrl1 (0x183).                                                              |  |  |  |  |  |

| 2019.01.17 | 3.4     | Remove the threshold for energy.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2019.11.29 | 3.5     | Add chip mark description.  Modify the maximum baud rate to 19200bps.                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 2020.08.10 | 3.7     | Add PN Junction Temperature.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

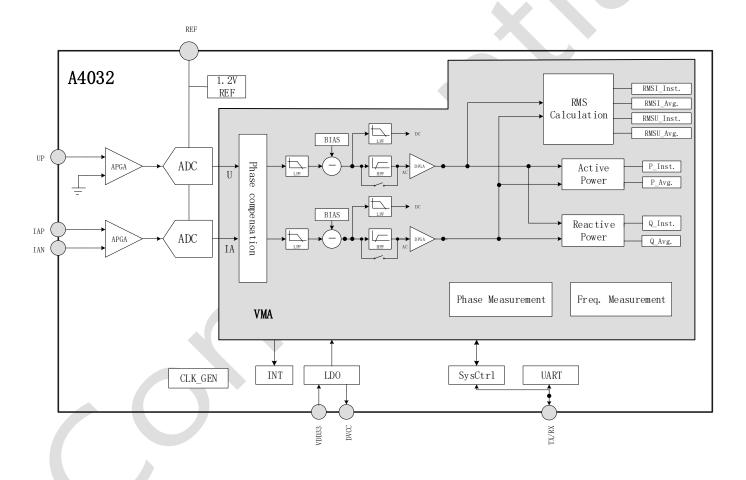

A4032 is a multifunction, ultralow power, single-phase power measurement IC with automatic baud rate adaption UART serial interface.

#### **Features**

- 3.3V power supply: 2.9V to 3.6V.

- Reference: 1.210V (typical drift 10ppm/°C).

- Typical power dissipation in full operation:

1.3mA (+-10%).

- Supporting one current channel for active and reactive energy metering simultaneously

- Highly metering accurate:

- ✓ Supporting IEC 62053-21:2003, IEC 62053-22:2003 and IEC 62053-23:2003;

- ✓ Less than 0.1% error for active/reactive energy metering over a dynamic range of 5000:1;

- 2 independent oversampling  $\Sigma/\Delta$  ADCs: one for voltage and one for current.

- Various measurements:

- ✓ DC components of voltage and current signals;

- ✓ Instantaneous /average current and voltage RMS;

- ✓ Instantaneous /average active/reactive power;

- ✓ Line frequency;

- ✓ Phase

- Automatic baud rate adaption UART interface, supporting baud rate: 1200bps~19200bps

- No input crystal required.

- Current input: Shunt resistor or CT

- Operating temperature: -40~+85°C.

- Storage temperature: -55~+150°C.

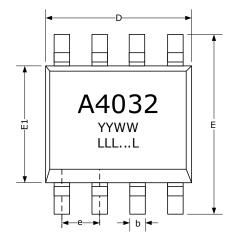

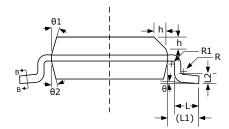

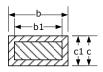

- Package: 8-SOP.

# **Pin Description**

| No. | Mnemonic | Туре             | Description                                                                                                                                                                      |

|-----|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD33    | Input            | 3.3V power supply. This pin must be connected to a $\geqslant 0.1 \mu F$ decoupling capacitor.                                                                                   |

| 2   | UP       | Input            | Positive input for Voltage Channel.                                                                                                                                              |

| 3   | IAN      | Input            | Negative input for Current Channel A.                                                                                                                                            |

| 4   | IAP      | Input            | Positive input for Current Channel A.                                                                                                                                            |

| 5   | REF      | Input<br>/Output | On-chip reference. This pin must be connected to a $1\mu\text{F}$ capacitor, and then grounded.                                                                                  |

| 6   | RX       | Input            | Receiver data input.  Hold low logic for at least 64ms to reset the chip.                                                                                                        |

| 6   | TX       | Output           | Transmitter data output                                                                                                                                                          |

| 7   | DVCC     | Output           | Digital power output. Should be connected to a parallel circuit combined by a $\geqslant$ 4.7uF capacitor and a 0.1uF decoupling capacitor, and then connected to analog ground. |

| 8   | VSS      | Ground           | Analog/digital ground.                                                                                                                                                           |

# **Specifications**

All maximum/minimum specifications apply over the entire recommended operation range (T=-40°C  $\sim$ +85°C, VDD33=3.3V $\pm$ 10%) unless otherwise noted. All typical specifications are at TA=25°C, VDD33=3.3V unless otherwise noted.

| Parameter                             | Min.         | Тур.  | Max. | Unit   | Remark                                                                    |  |  |

|---------------------------------------|--------------|-------|------|--------|---------------------------------------------------------------------------|--|--|

| Phase Error Between Channels          |              |       |      |        |                                                                           |  |  |

| PF=0.8 Capacitive                     |              | ±0.05 |      | Degree |                                                                           |  |  |

| PF=0.5 Inductive                      |              | ±0.05 |      | Degree |                                                                           |  |  |

| Active Energy Metering<br>Error       |              | 0.1   |      | %      | Dynamic Range 5000:1 @ 25°C  Fundamental frequency deviation within ± 25% |  |  |

| Active Energy Metering<br>Bandwidth   |              | 1.6   |      | kHz    |                                                                           |  |  |

|                                       |              |       |      |        | Dynamic Range 5000:1 @ 25°C                                               |  |  |

| Reactive Energy Metering Error        |              | 0.1   |      | %      | Fundamental frequency deviation within ± 25%                              |  |  |

| Reactive Energy Metering<br>Bandwidth |              | 1.6   |      | kHz    |                                                                           |  |  |

| VRMS Metering Error                   |              | 1     |      | %      | Dynamic Range 2000:1 @ 25°C  Fundamental frequency deviation within ± 25% |  |  |

| VRMS Metering Bandwidth               |              | 1.6   |      | kHz    |                                                                           |  |  |

| IRMS Metering Error                   |              | 1     |      | %      | Dynamic Range 5000:1 @ 25°C  Fundamental frequency deviation within ± 25% |  |  |

| IRMS Metering Bandwidth               |              | 1.6   |      | kHz    |                                                                           |  |  |

| Frequency Measurement                 |              |       |      |        |                                                                           |  |  |

| Range                                 | 40           |       | 70   | Hz     |                                                                           |  |  |

| Error                                 |              | 0.01  |      | Hz     |                                                                           |  |  |

| Analog Input                          | Analog Input |       |      |        |                                                                           |  |  |

| Maximum Signal Level                  |              |       | ±200 | mV     | Peak value                                                                |  |  |

| ADC                                   |              |       | T    | 1      |                                                                           |  |  |

| DC Offset                             |              |       | 10   | mV     |                                                                           |  |  |

|                                      |      | 1     |       | 1     |                              |

|--------------------------------------|------|-------|-------|-------|------------------------------|

| Parameter                            | Min. | Тур.  | Max.  | Unit  | Remark                       |

| Resolution                           |      | 23    |       | Bit   | Sign bit is included.        |

| Bandwidth (-3dB)                     |      | 1.6   |       | kHz   |                              |

| On-chip Reference                    |      |       |       |       |                              |

| Reference Error                      | -18  |       | 18    | mV    | @ 25°C                       |

| Power Supply Rejection<br>Ratio      |      | 80    |       | dB    |                              |

| Temperature Coefficient              |      | 10    | 30    | ppm/° |                              |

| Output Voltage                       |      | 1.210 |       | V     |                              |

| Power Supply                         |      |       |       |       |                              |

| VDD33                                | 2.9  | 3.3   | 3.6   | V     |                              |

| POR Detection Threshold              |      | 1.45  |       | V     | Error: ±10%                  |

| Power-Down Detection Threshold       | 2.5  | 2.7   | 2.9   | V     |                              |

| Digital Power Supply (DVCC           | )    |       |       |       | *                            |

| Voltage                              |      | 1.8   |       | V     | Programmable. Error: ±10%    |

| Current                              |      |       | 35    | mA    |                              |

| Logic Input                          | RX   |       |       |       |                              |

| Input High Voltage, V <sub>INH</sub> | 2.0  |       | 3.6   | V     |                              |

| Input Low Voltage, VINL              | -0.3 |       | 0.7   | V     |                              |

| Input Current, I <sub>IN</sub>       |      |       | 1     | μA    |                              |

| Input Capacitance, C <sub>IN</sub>   |      |       | 20    | pF    |                              |

| Baud Rate                            | 1200 |       | 19200 | bps   | Automatic baud rate adaption |

# **Absolute Maximum Ratings**

Operating circumstance exceeding Absolute Maximum Ratings may cause permanent damage to the device.

| Parameters           | Min. | Тур. | Max. | Unit | Description |

|----------------------|------|------|------|------|-------------|

| Digital Power Supply | -0.3 |      | +3.6 | V    | To ground.  |

| Analog Power Supply  | -0.3 |      | +3.6 | V    | To ground.  |

| Parameters                         | Min. | Тур. | Max. | Unit | Description |

|------------------------------------|------|------|------|------|-------------|

| Analog Input Voltage (IN/IP/UN/UP) | -0.3 |      | +3.3 | V    | To ground.  |

| Operating Temperature              | -40  |      | +85  | °C   |             |

| Storage Temperature                | -55  |      | +150 | °C   |             |

| PN Junction Temperature            | -40  |      | +125 | °C   |             |

# **Functional Block Diagram**

# **Table of Contents**

| ке  | vision H  | listory                         | ±  |

|-----|-----------|---------------------------------|----|

| Fe  | atures    |                                 | 2  |

| Pir | n Descrij | ption                           | 3  |

| Sp  | ecificati | ons                             | 4  |

| Ab  | solute M  | Maximum Ratings                 | 5  |

| Fu  | nctional  | Block Diagram                   | 6  |

| Та  | ble of Co | ontents                         | 0  |

| Fig | jure List | t                               | 2  |

|     |           |                                 |    |

| 1.  | Rese      | et                              | 5  |

|     | 1.1.      | Power-On Reset (POR)            |    |

|     | 1.2.      | RX Reset                        |    |

|     | 1.3.      | Global Software Reset           |    |

|     | 1.4.      | Registers                       |    |

| 2.  | Clock     | k                               | 8  |

|     | 2.1.      | 3.2768-MHz RC Oscillator        | 8  |

|     | 2.2.      | 32.768-kHz RC Oscillator        | 8  |

|     | 2.3.      | Registers                       | 9  |

| 3.  | Oper      | ration Mode                     | 11 |

|     | 3.1.      | Metering Mode                   | 11 |

| 4.  | Powe      | er Supply                       | 12 |

|     | 4.1.      | Power Supply Monitoring Circuit | 12 |

|     | 4.2.      | Power on Reset Circuit          | 13 |

| 5.  | Band      | lgap Circuit                    | 14 |

| 6.  | UART      | T Interface                     | 15 |

|     | 6.1.      | Data Byte                       | 15 |

|     | 6.2.      | Communication Protocol          | 15 |

|     | 6.2.      | .1. Write Operation             | 17 |

|     | 6.2.      | .2. Read Operation              | 17 |

|     | 6.2.      | .3. Broadcast Communication     | 19 |

| 7.  | Signa     | al Processing                   | 20 |

|     | 7.1.      | Analog Input                    | 20 |

|     | 7.2.      | Analog-to-Digital Conversion    | 22 |

|     | 7.3.      | Phase Compensation              | 22 |

|     | 7.4.      | Digital Input and DC Removal    | 24 |

|    | 7.5.  | RMS    | Calculation                      | 25 |

|----|-------|--------|----------------------------------|----|

|    | 7.5   | .1.    | RMS Calculation Equation         | 26 |

|    | 7.5   | .2.    | Gain Calibration of RMS          | 27 |

|    | 7.5   | .3.    | Offset Calibration of RMS        | 27 |

|    | 7.6.  | Powe   | er Calculation                   | 27 |

|    | 7.6   | .1.    | Gain Calibration of Power        | 28 |

|    | 7.6   | .2.    | Offset Calibration of Power      | 29 |

|    | 7.7.  | Line   | Frequency and Phase Measurement  | 29 |

|    | 7.7   | .1.    | Line Frequency Measurement       | 29 |

|    | 7.7   | .2.    | Voltage Phase Measurement        | 30 |

|    | 7.8.  | Calib  | pration                          | 31 |

|    | 7.8   | .1.    | Registers for Meter Calibration  | 31 |

|    | 7.8   | .2.    | Equations for Calibration        |    |

|    | 7.8   | .3.    | Calibration Steps                | 35 |

| 8. | Inte  | rrupt  |                                  | 38 |

| •  | 8.1.  | •      | iguration Verification Interrupt |    |

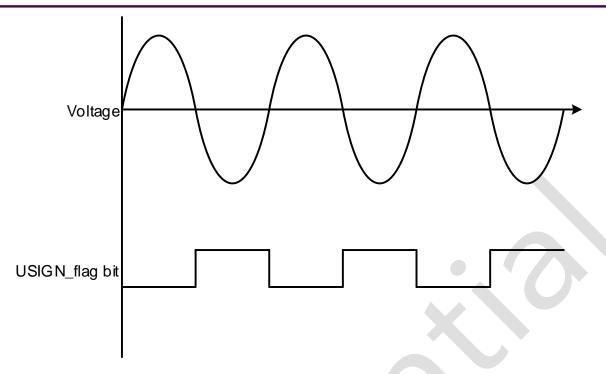

|    | 8.2.  |        | -Crossing Interrupt              |    |

|    | 8.3.  |        | sters                            |    |

|    |       | ,      |                                  |    |

| 9. | _     |        |                                  |    |

|    | 9.1.  |        | em Control Register              |    |

|    | 9.2.  |        | pration Parameter Registers      |    |

|    | 9.3.  | Chec   | cksum Register                   | 48 |

|    | 9.4.  | Soft   | ware Reset Control Register      | 48 |

|    | 9.5.  |        | em Status Registers              |    |

|    | 9.6.  | Mete   | ering Control Registers          | 52 |

| 10 | Outli | ine Di | imensions                        | 55 |

# **Figure List**

| Figure 1-1 Timing of POR                                                    | 5        |

|-----------------------------------------------------------------------------|----------|

| Figure 1-2 Timing of RX Reset                                               | 6        |

| Figure 1-3 Timing of Global Software Reset                                  | 7        |

| Figure 2-1 Clock Generation                                                 | 8        |

| Figure 4-1 Power Supply Architecture                                        | 12       |

| Figure 4-2 Power-Down Interrupt                                             | 13       |

| Figure 6-1 Structure of an 11-Bit Data Byte                                 | 15       |

| Figure 6-2 Command Frame for Read/Write/Broadcast Operation                 | 15       |

| Figure 6-3 Timing of UART Communication                                     | 16       |

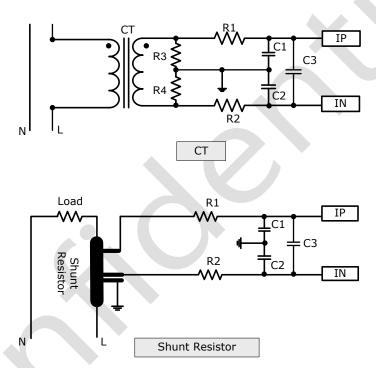

| Figure 7-1 Analog Input of Current Channel                                  | 20       |

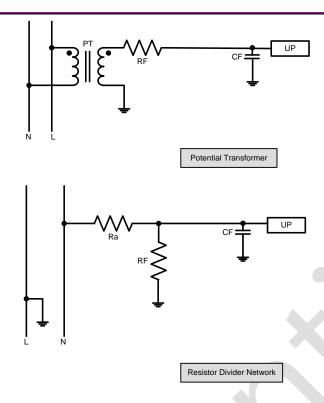

| Figure 7-2 Analog Input of Voltage Channel                                  | 21       |

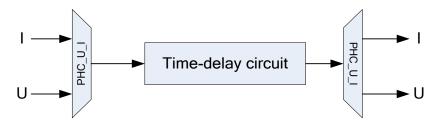

| Figure 7-3 Phase Compensation                                               | 23       |

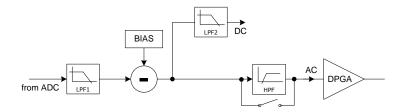

| Figure 7-4 Digital Input and DC Removal (Current Signal is taken as an Exan | nple) 24 |

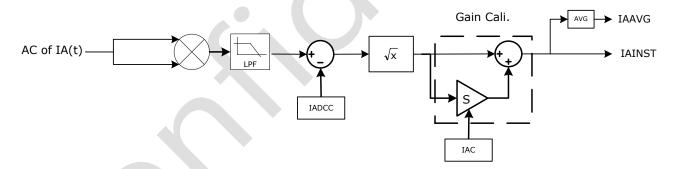

| Figure 7-5 RMS Signal Processing                                            | 25       |

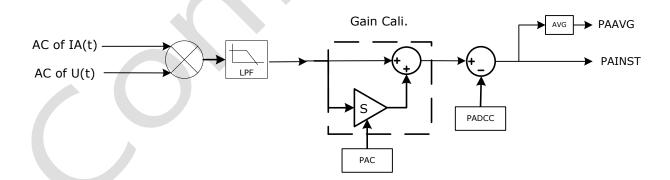

| Figure 7-6 Active Power Calculation                                         | 27       |

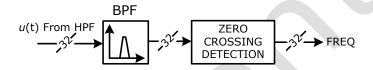

| Figure 7-7 Line Frequency Measurement Schematic Diagram                     | 29       |

| Figure 8-1 Zero-Crossing Interrupt                                          | 41       |

# **Table List**

| Table 1-1 Reset Related Registers                                                        | 7    |

|------------------------------------------------------------------------------------------|------|

| Table 2-1 Clock Generation Related Registers                                             | 9    |

| Table 3-1 States of Functional Units in Default State                                    | . 11 |

| Table 5-1 Configuration for Bandgap Circuit                                              | . 14 |

| Table 6-1 UART Communication Timing Parameters                                           | . 16 |

| Table 6-2 Structure of Data Byte (B7:B0) From Master MCU to A4032 on Write Operation     | . 17 |

| Table 6-3 Structure of Data Byte (B7:B0) From A4032 to Master MCU on Write Operation     | . 17 |

| Table 6-4 Structure of Data Byte (B7:B0) From Master MCU to A4032 on Read Operation      | . 18 |

| Table 6-5 Structure of Data Byte (B7:B0) From A4032 to Master MCU on Read Operation      | . 18 |

| Table 6-6 Structure of Data Byte (B7:B0) From Master MCU to A4032 on Broadcast Operation |      |

|                                                                                          |      |

| Table 7-1 Analog PGA Configuration                                                       |      |

| Table 7-2 Analog Control Register 0 (0x0182, AnaCtrl0, R/W)                              | . 22 |

| Table 7-3 Analog Control Register 1 (0x0183, AnaCtrl1, R/W)                              | . 22 |

| Table 7-4 Enable/Disable ADCs of Each Channel                                            | . 22 |

| Table 7-5 Registers for phase compensation                                               | . 23 |

| Table 7-6 $f_{smpl}$ Determines Phase Compensation Resolution and Correction Range       | . 23 |

| Table 7-7 DC Component Calculation Related Register                                      | . 25 |

| Table 7-8 Digital Gain Configuration of Voltage Signal                                   | . 25 |

| Table 7-9 RMS Related Registers                                                          | . 25 |

| Table 7-10 Power Related Registers                                                       | . 28 |

| Table 7-11 Bandpass Filter Parameters                                                    | . 30 |

| Table 7-12 Voltage Frequency Data Register                                               | . 30 |

| Table 7-13 Phase Measurement Related Register (R)                                        | . 30 |

| Table 7-14 Meter Calibration Related Registers                                           | . 31 |

| Table 8-1 Interrupt Flag Bits                                                            | . 38 |

| Table 8-2 Registers for Configuration Verification                                       | . 39 |

| Table 8-3 System Status Clr Register (0x019D, SysStsClr, R/W)                            | . 41 |

| Table 9-1 System Control Register (0x0180, SysCtrl, R/W),                                | . 42 |

| Table 9-2 Analog Control Register 0 (0x0182, AnaCtrl0, R/W)                              | . 45 |

| Table 9-3 Analog Control Register 1 (0x0183, AnaCtrl1, R/W)                   | 45                |

|-------------------------------------------------------------------------------|-------------------|

| Table 9-4 Power/RMS/Low-Current Signal Calibration/Phase Calibration Register | ( <b>R/W</b> ) 46 |

| Table 9-5 Checksum Register (0x0109, CKSUM, R/W)                              | 48                |

| Table 9-6 Software Reset Control Register (0x01BF, SFTRST, W)                 | 48                |

| Table 9-7 System Status Register (0x00CA, SysSts, R)                          | 49                |

| Table 9-8 System Status Clr Register (0x019D, SysStsClr, R/W)                 | 51                |

#### 1.Reset

In the A4032, the chip will be reset to Default State when POR, RX reset or global software reset occurs.

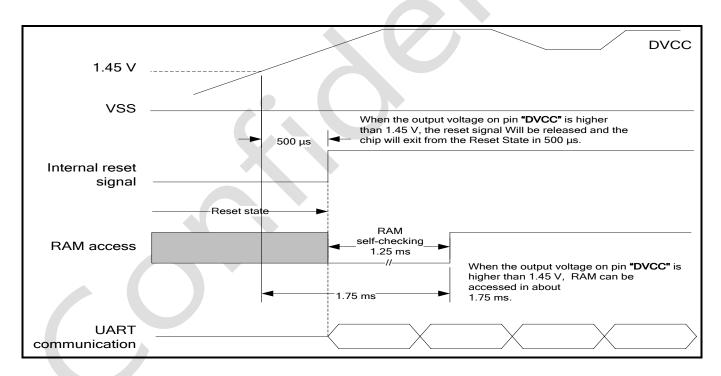

#### 1.1. Power-On Reset (POR)

In the A4032, the internal power-on reset circuit supervises the output voltage on pin DVCC all the time. When the output voltage is lower than 1.45V, the reset signal is generated and forces the chip into reset state. When the output voltage is higher than 1.45V, the reset signal is released and the chip will get to Default State in  $500\mu s$ .

When POR event occurs, bit RSTSRC (bit[5:3] of SysSts, 0x00CA) is reset to 0b001.

In the reset state, the master MCU and the specific metering architecture cannot access the RAM. When the chip exits from the reset state, the RAM will implement self-check in about 1.25ms. If no error occurs, the RAM can be accessed.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip exits from the reset state.

Figure 1-1 Timing of POR

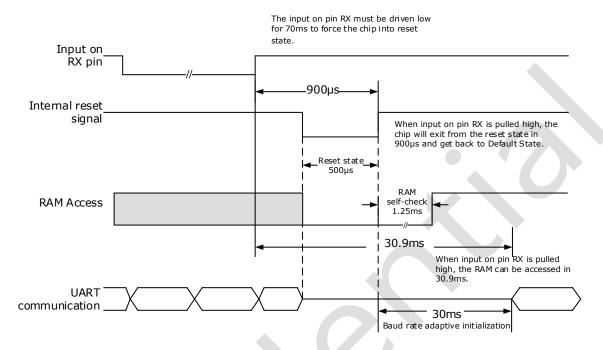

#### 1.2. RX Reset

The input on pin RX must be driven low for at least 70ms to force the chip into the reset state. Pull the logic high, and 900µs later the chip exits from the reset state and gets back to Default State.

When RX reset occurs, bit RSTSRC (bit[5:3] of SysSts, 0x00CA) is reset to 0b011.

In the reset state, the master MCU and the specific metering architecture cannot access the RAM. When the chip exits from the reset state, the RAM will implement self-check in about 1.25ms. If no error occurs, the RAM can be accessed in 30.9ms later after RX reset.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip exits from the reset state.

Figure 1-2 Timing of RX Reset

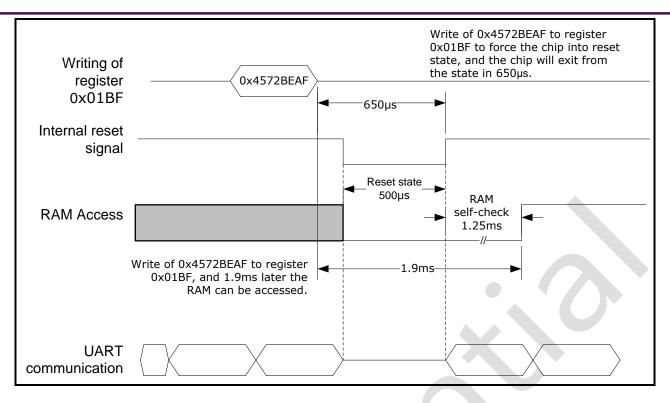

#### 1.3. Global Software Reset

In the A4032, writing of 0x4572BEAF in the register SFTRST (0x01BF) can force the chip into the reset state, and the chip will exit and get back to Default State in  $650\mu s$ .

When global software reset occurs, bit RSTSRC(bit[5:3]of SysSts, 0x00CA) is reset to 0b100.

In the reset state, the master MCU and the specific metering architecture cannot access the RAM. When the chip exits from the reset state, the RAM will implement self-check in about 1.25ms. If no error occurs, the RAM can be accessed.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip exits from the reset state.

**Figure 1-3 Timing of Global Software Reset**

## 1.4. Registers

Table 1-1 Reset Related Registers

| Register                             | Bit      | Description |        |                                                                                   |                                   |  |  |  |  |

|--------------------------------------|----------|-------------|--------|-----------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

|                                      |          | Flag b      | its to | indicat                                                                           | te the reset source.              |  |  |  |  |

|                                      |          | Bit5        | Bit4   | Bit3                                                                              | Description                       |  |  |  |  |

| 0x00CA                               | Bit[5:3] | 0           | 0      | 1                                                                                 | A POR event occurred.             |  |  |  |  |

| SysSts                               | RSTSRC   | 0           | 0      | 0                                                                                 | Reserved.                         |  |  |  |  |

| 3,5565                               |          | 0           | 1      | 1                                                                                 | An RX reset event occurred.       |  |  |  |  |

|                                      |          | 0           | 1      | 0                                                                                 | Reserved.                         |  |  |  |  |

|                                      |          | 1           | 0      | 0                                                                                 | A global software reset occurred. |  |  |  |  |

| 0x01BF, SF<br>Software R<br>Register |          |             |        | able, in the form of 32-bit 2's complement.  To the register to reset the system. |                                   |  |  |  |  |

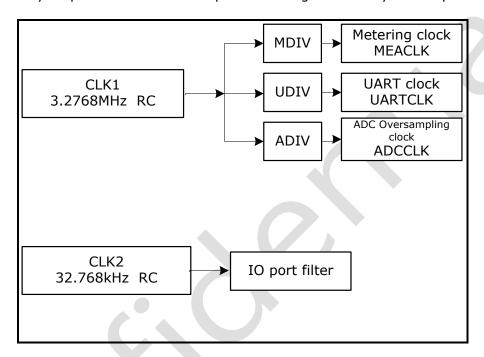

#### 2.Clock

There are 2 on-chip RC oscillation circuits (3.2MHz/32KHz) provide clocks for the A4032:

- On-chip 3.2768MHz RC oscillator generates the clock (CLK1) that works as a clock source for the specific metering architecture (VMA), ADCs and UART serial interface. This circuit can be disabled. After POR, RX reset or global software reset, this circuit will be enabled automatically.

- On-chip 32.768kHz RC oscillator generates the clock (CLK2) that works as the clock source for the filters for some key IO ports. This circuit keeps on working until the system is powered off.

Figure 2-1 Clock Generation

#### 2.1. 3.2768-MHz RC Oscillator

In the A4032, an on-chip 3.2768MHz RC oscillator is designed to generate a 3.2768-MHz (The deviation is within  $\pm$  20% from chip to chip for mass production. The temperature deviation from -40~85 degree for each specific chip is less than 3%.) clock (CLK1) to work as a clock source for the specific metering architecture, ADCs and UART serial interface.

#### 2.2. 32.768-kHz RC Oscillator

The on-chip 32.768-kHz RC oscillator can generate a 32.768kHz RC clock (CLK2) for the filters for some key IO ports. This oscillator cannot be disabled until the system is powered off.

## 2.3. Registers

**Table 2-1 Clock Generation Related Registers**

| Register          | Bit                       | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Bit[21:20] ADCCLKSEL<1:0> | 2′b00   | To select the sampling frequency of the oversampling ADC (ADC clock, ADCCLK). The sampling frequency of the ADCs must be a quarter or one eighth of the metering clock (MEACLK) frequency when the chip operates with full functions in Metering Mode.  00: 819.2kHz; 01: 409.6kHz; 10: 204.8kHz; 11: 102.4kHz.  When the chip operates with full functions in Metering Mode, their default values are recommended to be used for the best performance. |

| 0x0180<br>SysCtrl | Bit19<br>MEACLKSEL        | 0       | To select the clock frequency for the specific metering architecture (MEACLK).  0: 3.2768MHz; 1: 819.2kHz.  The sampling frequency of the ADCs must be a quarter or one eighth of the metering clock (MEACLK) frequency when the chip operates with full functions in Metering Mode.                                                                                                                                                                    |

|                   | Bit[11:7]  RCTRIM<4:0>    | 0       | Adjust the internal high frequency RC clock frequency (Default value is 3.2768MHz.). The default 0b00000 is not adjusted. For the normal metering, it is recommended to write default values for best performance. From "0b00001" to "0b01111", the RC clock frequency is decreased by 2% per LSB.  From "0b11111" to "0b10000", the RC clock frequency is increased by 2% per LSB.                                                                     |

| Register | Bit           | Default | Description                                                                                                                                                                                                                                       |

|----------|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Bit6<br>RCX12 | 0       | RC frequency adjustment. The default frequency of the metering chip is 50Hz. When the 60Hz system is applied, users can increase the high frequency RC clock default frequency of 3.2MHZ to 1.2 times of the original.  0: No adjustment  1: X1.2 |

## 3. Operation Mode

When the chip is working, it can be reset to Default State when POR, RX reset, or global software reset occurs. Table 3-1 lists the states of functional units in the A4032 in Default State.

In Default State, the typical load current is  $500\mu A$ . Some easy configuration can drive the chip to work in Metering Mode.

**Table 3-1 States of Functional Units in Default State**

| Functional Unit                 | Default State                                     |

|---------------------------------|---------------------------------------------------|

| 3.2MHz RC oscillator            | Enabled.                                          |

| 32kHz RC oscillator             | Enabled.                                          |

| Bandgap circuit                 | Enabled.                                          |

| Biasing circuit                 | Enabled.                                          |

| Power supply monitoring circuit | Enabled.                                          |

| POR circuit                     | Enabled.                                          |

| LDO                             | Enabled.                                          |

| ADC                             | Disabled.                                         |

| Specific metering architecture  | Enabled, but for configuration verification only. |

| UART serial interface           | Enabled.                                          |

## 3.1. Metering Mode

In Default State, the A4032 will enter Metering Mode via some easy configuration:

- to enable or disable the ADCs, to configure the sampling frequency to 819.2kHz or 204.8kHz;

- to configure MEACLK frequency to 3.2768MHz or 819.2kHz; the operating mode can be configured to enable only the parameter configuration self-checking or to achieve all functions.

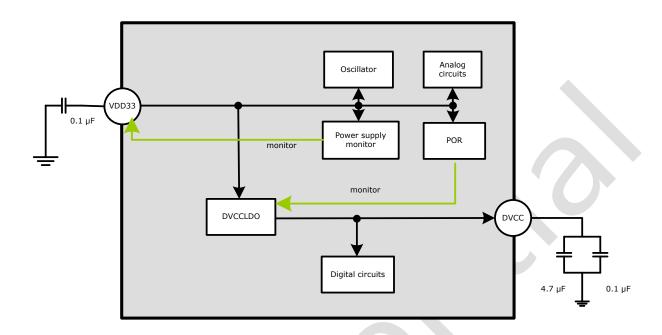

## 4. Power Supply

**Figure 4-1 Power Supply Architecture**

The A4032 supports a power input 3.3V.

The VDD33 is for the digital circuit power supply, and for the analog circuit power supply, oscillator, power-on reset, and power-down detection circuit are integrated. The connection among the modules as shown above.

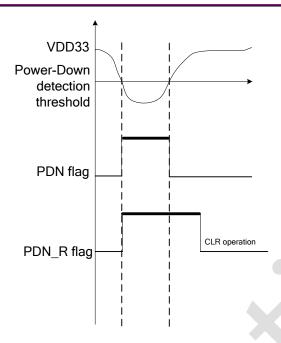

#### 4.1. Power Supply Monitoring Circuit

In the A4032, an internal power supply monitoring circuit is designed to supervise the power input on pin VDD33. When the input on pin VDD33 is less than Power-Down detection threshold, a power-down interrupt signal is triggered, and the flag bit PDN (bit7 of SysSts) and PDN\_R(bit6 of SysSts) are set to 1. When the power down event disappears, the flag bit PDN will be cleared automatically and PDN\_R(bit6 of SysSts) should be cleared manually

**Figure 4-2 Power-Down Interrupt**

#### 4.2. Power on Reset Circuit

In the A4032, the internal power-on reset circuit supervises the output voltage on pin DVCC all the time. When the output voltage is lower than 1.45V, the reset signal is generated and forces the chip into reset state. When the output voltage is higher than 1.45V, the reset signal is released. Please refer to 1.1 Power-On Reset (POR).

## 5.Bandgap Circuit

In the A4032, the Bandgap circuit outputs a reference voltage and bias voltage, about 1.210V with a typical temperature coefficient of 10ppm/°C, for ADCs and the 3.2MHz RC oscillator.

By default the Bandgap circuit is enabled.

Users can configure bit[18:16]( REST<2:0>) and bit[15:14]( RESTL<1:0>) of SysCtrl (0x0180) to adjust the temperature coefficient to compensate the temperature coefficient error introduced by the external components with the following steps:

- 1) Assume the current settings of relative bits are REST<2:0>='010' and RESTL<1:0>='00', which means an additional +20ppm for temperature coefficient of Bandgap.

- 2) Measure meter errors in high and low temperature conditions. Assume user has calibrated the meter error to 0 at  $20^{\circ}$ C, and the measuring errors are 0.6% at  $80^{\circ}$ C and -0.4% at  $-40^{\circ}$ C separately. Then a -(0.6%-(-0.4%))/2=-0.5% measuring error needs to be compensated relative to high temperature working condition, equivalent to -0.5%/(80-20)=-5000/60=-83ppm, rounding to -80ppm.

- 3) As measuring error is minus two times of REF temperature coefficient error, to compensate a -80ppm error, an additional +40ppm of Bandgap REF temperature coefficient adjustment is needed. Taking the initial +20ppm setting into consideration, the actual adjustment should be +60ppm. According to the lookup table of RESTL<1:0> and REST<2:0>, user should set register RESTL<1:0> to '01' and REST<2:0> to '111', whose combination equals to a +60ppm temperature coefficient adjustment.

A temperature coefficient drift of x in the Bandgap circuit results in a drift of -2x in the measurement error.

Table 5-1 Configuration for Bandgap Circuit

| Register | bit                   | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysCtrl  | Bit[18:16] REST<2:0>  | To finely adjust the temperature coefficient of the Bandgap circuit. In order to obtain the best metering performance and temperature performance during normal metering, it must be configured according to the calculated result. The calculation method, please refer to Bandgap Circuit chapter.  000: no adjustment; 001: +10ppm; 010: +20ppm; 011: +30ppm; 100: -40ppm; 101: -30ppm; 110: -20ppm; 111: -10ppm. |

| 0x0180   | Bit[15:14] RESTL<1:0> | To roughly adjust the temperature coefficient of the Bandgap circuit. In order to obtain the best metering performance and temperature performance during normal metering, it must be configured according to the calculated result. The calculation method, please refer to Bandgap Circuit chapter.  00: 0; 01: +70ppm; 10: -140ppm; 11: -70ppm.                                                                   |

#### **6.UART Interface**

The A4032 supports communication with the master MCU as a slave via UART serial interface. The UART serial interface has features:

- Asynchronous, half-duplex communication;

- A 11-bit data byte, composed of 1-bit Start bit, 8-bit Data bits, 1-bit Parity bit (odd), and 1-bit Stop bit;

- Least significant bit (LSB) shifted in or out firstly when the chip receives or transmits a byte;

- Automatic baud rate adaption: support 1200bps<sup>~</sup>19200bps, and typical baud rates are 1200bps, 2400bps, 4800bps, 9600bps, and 19200bps.

When a reset event, such as POR, RX reset or global software reset, occurs, the UART serial interface is reset.

#### 6.1. Data Byte

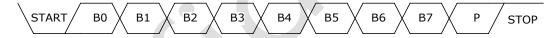

The data byte received and transmitted via the UART serial interface of the A4032 is composed of 11 bits, including 1-bit Start bit (logic low), 8-bit Data bits, 1-bit odd Parity bit and 1-bit Stop bit (logic high), as shown in the following figure. When the A4032 receives or sends a data byte, the least significant bit always is shifted in or out firstly.

Figure 6-1 Structure of an 11-Bit Data Byte

#### 6.2. Communication Protocol

In read, write or broadcast communication, the master MCU needs a command frame that is composed of 8 data bytes to operate a 32-bit data in the A4032.

| Hea | d Byte | Control Byte | Address<br>Byte | Data Byte 0 | Data Byte 1 | Data Byte 2 | Data Byte 3 | Check Byte |

|-----|--------|--------------|-----------------|-------------|-------------|-------------|-------------|------------|

|-----|--------|--------------|-----------------|-------------|-------------|-------------|-------------|------------|

Figure 6-2 Command Frame for Read/Write/Broadcast Operation

In read or write operation, when the A4032 receives the command frame from the master MCU, it will reply to the master MCU with a respond frame of different structures. In broadcast communication, the A4032 will not reply to the master MCU to avoid communication conflict.

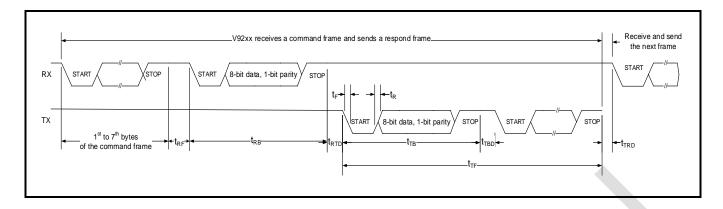

The following figure depicts the timing of UART communication.

**Figure 6-3 Timing of UART Communication**

**Table 6-1 UART Communication Timing Parameters**

| Parameter        | Description                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Time to receive a data byte on pin RX.                                                                                                                                                 |

| t <sub>RB</sub>  | $t_{RB} = \frac{11}{baudrate}$                                                                                                                                                         |

|                  | Where, baudrate is the actual baud rate.                                                                                                                                               |

|                  | The maximum time between two bytes when receiving a command frame on pin "RX"                                                                                                          |

| t <sub>RF</sub>  | t <sub>RF</sub> =20ms                                                                                                                                                                  |

|                  | After a timeout event, the UART interface is idle and waits for the next command frame.                                                                                                |

|                  | The delay between command frame reception on pin RX and respond frame transmission on pin TX.                                                                                          |

| t <sub>RTD</sub> | 1ms≤t <sub>RTD</sub> ≤20ms                                                                                                                                                             |

| 100              | Please note no respond frame will be transmitted in broadcast communication, and at least 1ms delay is recommended between two continuous command frames for broadcast communications. |

| tтғ              | Time to transmit a respond frame in read or write operation, depending on the structure of the frame.                                                                                  |

|                  | Time to transmit a data byte.                                                                                                                                                          |

| tтв              | $t_{TB} = \frac{11}{baudrate}$                                                                                                                                                         |

|                  | Where baudrate is the actual baud rate.                                                                                                                                                |

| _                | Delay between two continuous data bytes in a respond frame.                                                                                                                            |

| T <sub>TBD</sub> | 0ms≤t <sub>TBD</sub> ≤20ms                                                                                                                                                             |

| t <sub>TRD</sub> | The delay between respond frame transmission on pin TX and the next command frame reception on pin RX. More than 1ms is recommended.                                                   |

| Parameter      | Description                          |

|----------------|--------------------------------------|

| t <sub>R</sub> | Rise time of RX and TX, about 300ns. |

| t <sub>F</sub> | Fall time of RX and TX, about 300ns. |

#### 6.2.1. Write Operation

The master MCU needs a command frame, composed of 8 data bytes, to write of a 32-bit data to the register of the A4032. When it receives the command frame, the A4032 will transmit a respond frame, composed of 4 data bytes, to reply to the master MCU. On both transmission and reception, the LSB is shifted in or out firstly.

Table 6-2 Structure of Data Byte (B7:B0) From Master MCU to A4032 on Write Operation

|       | Tubico I ou usual con out and a procession of the contract of |               |                                 |                 |                 |        |          |        |         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------|-----------------|-----------------|--------|----------|--------|---------|

| Order | Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B7            | B6                              | B5              | B4              | В3     | B2       | B1     | В0      |

| 1     | Head Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0             | 1                               | 1               | 1               | 1      | 1        | 0      | 1       |

| 2     | Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The higher 4  | bits of the ta                  | arget register  | address.        | 0      | 0        | 1      | 0       |

| 3     | Address Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The lower 8   | bits of the tar                 | rget register a | address.        |        |          |        |         |

| 4     | Data Byte 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit[7:0] of t | Bit[7:0] of the target data.    |                 |                 |        |          |        |         |

| 5     | Data Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit[15:8] of  | the target da                   | ta.             |                 |        |          |        |         |

| 6     | Data Byte 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit[23:16] o  | f the target d                  | ata.            |                 |        |          |        |         |

| 7     | Data Byte 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit[31:24] o  | f the target d                  | ata.            |                 |        |          |        |         |

| 8     | Check Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | m. Add the at<br>ain the checks | •               | ytes, invert th | e sum, | , and th | nen ad | d it to |

Table 6-3 Structure of Data Byte (B7:B0) From A4032 to Master MCU on Write Operation

| Order | Byte         | B7          | B6            | B5           | B4             | В3       | B2      | B1      | В0       |

|-------|--------------|-------------|---------------|--------------|----------------|----------|---------|---------|----------|

| 1     | Head Byte    | 0           | 1             | 1            | 1              | 1        | 1       | 0       | 1        |

| 2     | Control Byte | The higher  | 4 bits of the | target regis | ster address.  | 0        | 0       | 1       | 0        |

| 3     | Address Byte | The lower 8 | bits of the t | arget regist | er address.    |          |         |         |          |

| 4     | Check Byte   |             | um. Add the a |              | a bytes, inver | t the su | ım, and | then ac | dd it to |

#### 6.2.2. Read Operation

The master MCU needs a command frame, composed of 8 data bytes, to read of a 32-bit data of a register of the A4032. When it receives the command frame, the A4032 will transmit a respond frame,

composed of  $4\times N+4$  ( $1\leq N\leq 255$ ) data bytes, to reply to the master MCU. On both transmission and reception, the LSB is shifted in or out firstly.

Table 6-4 Structure of Data Byte (B7:B0) From Master MCU to A4032 on Read Operation

| Order | Byte         | B7                                                                         | B6                                                                | B5                                                                                       | B4                                                                         | В3                                        | B2                                               | B1            | В0                                 |

|-------|--------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------|---------------|------------------------------------|

| 1     | Head Byte    | 0                                                                          | 1                                                                 | 1                                                                                        | 1                                                                          | 1                                         | 1                                                | 0             | 1                                  |

| 2     | Control Byte | The higher 4                                                               | bits of the ta                                                    | rget register a                                                                          | address (D <sub>1</sub> ).                                                 | 0                                         | 0                                                | 0             | 1                                  |

| 3     | Address Byte | The lower 8                                                                | bits of the tai                                                   | rget register a                                                                          | address (D <sub>1</sub> ).                                                 |                                           |                                                  |               |                                    |

| 4     | Data Byte 0  | at the addre Byte and Add is read out. When the m When more the target add | aster MCU reathan one registers (D <sub>1</sub> ), N 255, which m | ng with the ta<br>hen Data Byte<br>ads of the tare<br>sters located a<br>is equal to the | ta to be read to rget address of the continuous enumber of the than 255 co | $(D_1)$ gi<br>ans 1 d<br>nly, N<br>addres | ven by<br>lata wo<br>is 1.<br>sses be<br>ess. Th | the Cord (4 b | ontrol<br>oytes)<br>g with<br>imum |

| 5     | Data Byte 1  |                                                                            |                                                                   |                                                                                          |                                                                            |                                           |                                                  |               |                                    |

| 6     | Data Byte 2  | No actual fu                                                               | nction.                                                           |                                                                                          |                                                                            |                                           |                                                  |               |                                    |

| 7     | Data Byte 3  |                                                                            |                                                                   |                                                                                          |                                                                            |                                           |                                                  |               |                                    |

| 8     | Check Byte   |                                                                            | m. Add the al                                                     |                                                                                          | ytes, invert th                                                            | e sum,                                    | , and th                                         | nen ad        | d it to                            |

Table 6-5 Structure of Data Byte (B7:B0) From A4032 to Master MCU on Read Operation

|       | ible of betracture of batta byte (bribb) from A 1002 to Haster free on Reda operation |                                |                                                                    |              |                                         |                     |        |         |        |

|-------|---------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------|--------------|-----------------------------------------|---------------------|--------|---------|--------|

| Order | Byte                                                                                  | B7                             | В6                                                                 | B5           | B4                                      | В3                  | B2     | B1      | В0     |

| 1     | Head Byte                                                                             | 0                              | 1                                                                  | 1            | 1                                       | 1                   | 1      | 0       | 1      |

| 2     | Control Byte                                                                          | The higher 4 b                 | its of the tar                                                     | get register | address $(D_1)$ .                       | 0                   | 0      | 0       | 1      |

| 3     | Length Byte                                                                           | N, equal to Da<br>When Data By | •                                                                  |              | naster MCU to                           | A4032               | on rea | ad oper | ation. |

| 4     | Data Byte 10                                                                          | Bit[7:0] of the                | register loc                                                       | ated at targ | jet address (D <sub>1</sub>             | ).                  |        |         |        |

| 5     | Data Byte 11                                                                          | Bit[15:8] of th                | e register lo                                                      | cated at tar | rget address (E                         | ) <sub>1</sub> ).   |        |         |        |

| 6     | Data Byte 12                                                                          | Bit[23:16] of t                | he register l                                                      | ocated at ta | arget address (                         | (D <sub>1</sub> ).  |        |         |        |